# Linear Charger for 1Cell Li-ion Battery with System-path IC Monolithic IC MM3538AL

### Outline

This IC is a linear charging control IC with built-in system paths, and includes a chip with system path function and lithium ion/lithium polymer secondary battery charging function.

This IC features a built-in load switch with overvoltage detection function and input current limit required for system paths, and built-in power FETs, backflow prevention diodes, and current sensor function required for charging and discharging.

The IC comes equipped with an adapter and USB automatic recognition function, and allows the individual settings for charging control voltage and current with I<sup>2</sup> C communication.

### Features

- (1) ADP/USB detection by using of USB bus

- (2) I<sup>2</sup>Cbus control

- (3) Support for JEITA

D+/D- pin CC/CV/Charge ON/OFF battery temperature profile

- (4) System path current limit of ADP mode is adjustable by ILIM pin

- (5) 24V High Voltage torelance(IN pin)

- (6) Support for operating system out from battery (built-in low on resistance FET)

- (7) Linear charger control for Li-ion, Li-pol

- (8) Charge current setting by ISET pin

- (9) Charge timer setting by TMR pin

- (10) Indicator : Input power connected

(INGOOD pin) Charge condition (CHG pin) BAT voltage condition (OUTGOOD pin) I<sup>2</sup>C alarm(SAL pin).

### Package

WLCSP-25A

### Applications

- (1) Tablets

- (2) Smartphones

- (3) Digital still cameras

- (4) Portable music players

- (5) Portable games

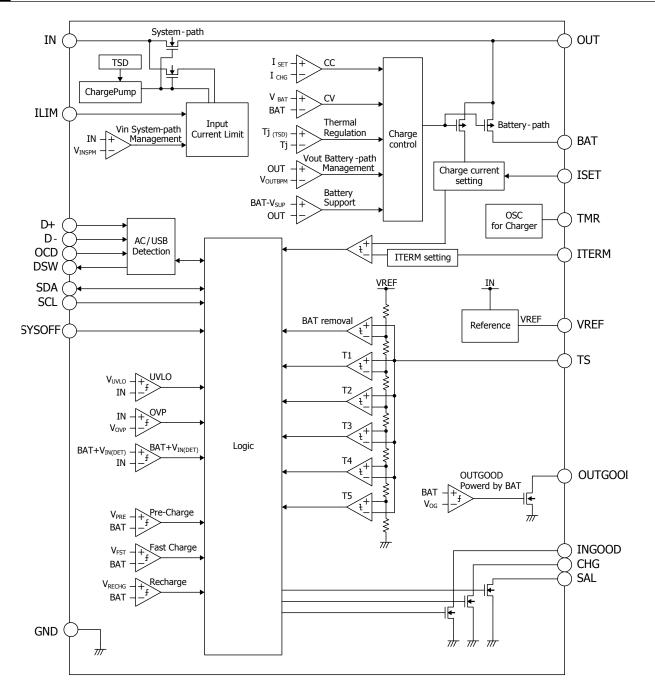

## Block diagram

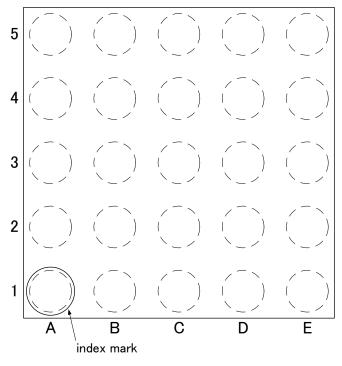

# Pin assinmet

(TOP VIEW)

| Pin No.        | Function |

|----------------|----------|

| A1             | IN       |

| A2             | ILIM     |

| A3             | D-       |

| A4             | D+       |

| A5             | GND      |

| B1             | INGOOD   |

| B2             | OCD      |

| B3             | DSW      |

| B4             | SAL      |

| B5             | OUTGOOD  |

| C1<br>C2<br>D2 | OUT      |

| C3             | ISET     |

| C4             | SDA      |

| C5             | TMR      |

| D1<br>E1<br>E2 | BAT      |

| D3             | TS       |

| D4             | SCL      |

| D5             | CHG      |

| E3             | VREF     |

| E4             | SYSOFF   |

| E5             | ITERM    |

# **Pin Description**

| Pin No.        | Symbol  | Function                                                                                             |

|----------------|---------|------------------------------------------------------------------------------------------------------|

| A1             | IN      | Power supply input pin that connects AC adaptor or USB.                                              |

| A2             | ILIM    | System-path current limit setting. Connect a resistor between this pin and GND.                      |

| A3             | D-      | USB bus D- input.                                                                                    |

| A4             | D+      | USB bus D+ input.                                                                                    |

| A5             | GND     | Ground pin.                                                                                          |

| B1             | INGOOD  | Input OK indicator. NchMOS open drain output.                                                        |

| B2             | OCD     | Default System-path current limit setting when USB detected. Input H/L.                              |

| B3             | DSW     | Control pin for external USB signal switch. Inverter output.                                         |

| B4             | SAL     | I <sup>2</sup> C alarm indicator. NchMOS open drain output.                                          |

| B5             | OUTGOOD | Output OK indicator. NchMOS open drain output.                                                       |

| C1<br>C2<br>D2 | OUT     | System-path output pin. Output power to the system.                                                  |

| C3             | ISET    | Charge current setting pin. Connec a resistor between this pin and GND.                              |

| C4             | SDA     | I <sup>2</sup> C data input and output pin.                                                          |

| C5             | TMR     | Oscillator frequency setting pin for the charge timer. Connect a capacitor between this pin and GND. |

| D1<br>E1<br>E2 | BAT     | Li-ion battery connection pin. Charging to Li-ion battery and discharging to OUT pin.                |

| D3             | TS      | Thermistor input pin. Connect the terminal of the battery pack thermistor.                           |

| D4             | SCL     | I <sup>2</sup> C clock input pin.                                                                    |

| D5             | CHG     | Charge status indicator. NchMOS open drain output.                                                   |

| E3             | VREF    | Battery thermistor reference voltage output. Connect TS pin through a resistor.                      |

| E4             | SYSOFF  | Turn off System-path. Input H/L.                                                                     |

| E5             | ITERM   | End-of-charge current setting pin. Connect a resistor between this pin and GND.                      |

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

## Absolute Maximum Ratings

| (Except where noted otherwise : Ta=25°C |                     |                  |       |  |  |  |

|-----------------------------------------|---------------------|------------------|-------|--|--|--|

| Item                                    | Symbol              | Ratings          | Units |  |  |  |

| Storage temperature                     | Tstg                | –55 $\sim$ +150  | °C    |  |  |  |

| Junction temperature                    | Тјмах               | $-40 \sim +150$  | °C    |  |  |  |

| IN pin input voltage                    | VHin <sub>MAX</sub> | –0.3 $\sim$ +24  | V     |  |  |  |

| Other pin input voltage                 | Vin <sub>MAX</sub>  | –0.3 $\sim$ +6.0 | V     |  |  |  |

| IN pin input current                    | IIN <sub>MAX</sub>  | $\sim$ 2.0       | А     |  |  |  |

| OUT pin output current                  | IOUT <sub>MAX</sub> | $\sim 5$         | А     |  |  |  |

| BAT pin input and output current        | IBAT <sub>MAX</sub> | $\sim 5$         | A     |  |  |  |

| Power dissipation(*1)                   | Pd                  | ~ 1.0            | W     |  |  |  |

(\*1) Board size :  $80mm \times 70mm \times 1.6mm$  Material : grass epoxy Layer : 2Layers Wire rate : 90%

## **Recommended Operation Conditions**

|                                   | (Except where noted otherwise : Ta=25°C , IN |                 |       |  |  |  |

|-----------------------------------|----------------------------------------------|-----------------|-------|--|--|--|

| Item                              | Symbol                                       | Ratings         | Units |  |  |  |

| Operating ambient temperature(*2) | Topr                                         | -40 ~ +85       | C     |  |  |  |

| Junction temperature              | Tj                                           | -40 ~ +125      | C     |  |  |  |

| IN pin input voltage              | VHin                                         | $4.35 \sim 5.5$ | V     |  |  |  |

| Other pin input voltage           | Vin                                          | $0 \sim 5.5$    | V     |  |  |  |

| ILIM setting resistance           | RILIM                                        | 40 ~ 400        | kΩ    |  |  |  |

| ISET setting resistance           | RISET                                        | 53.33 ~ 400     | kΩ    |  |  |  |

| ITERM setting resistance          | RITERM                                       | 40 ~ 400        | kΩ    |  |  |  |

| TMR setting capacitor             | Стмг                                         | 5 ~ 50          | nF    |  |  |  |

(\*2) Board size : 80mm × 70mm × 1.6mm Material : grass epoxy Layer : 2Layers Wire rate : 90%

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

# **Electrical Characteristics**

| (Except where noted otherwise ∶Ta=25℃, IN       |                          |                                                                                                |      |      |      | C, IN=5V) |

|-------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------|------|------|------|-----------|

| Item                                            | Symbol                   | Measurement conditions                                                                         | Min. | Тур. | Max. | Units     |

| POWER SUPPLY INPUT                              |                          |                                                                                                |      |      |      |           |

| Consumption current 1                           | lcc                      | IN=5V, SYSOFF="L"<br>IN pin input current                                                      |      | 1.2  | 2.0  | mA        |

| Consumption current 2                           | ICCOFF                   | IN=5V, SYSOFF="H"<br>IN pin input current                                                      |      | 300  | 500  | uA        |

| Consumption current 3                           | ICCBAT                   | BAT=4.2V, IN=0V<br>BAT pin input current                                                       |      | 4    | 10   | uA        |

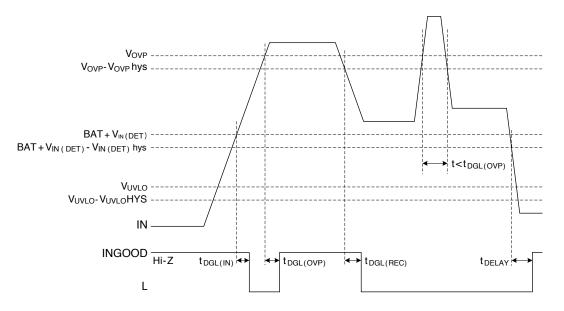

| Under voltage lock-out                          | V <sub>UVLO</sub>        | IN=L → H                                                                                       | 3.1  | 3.2  | 3.3  | v         |

| Hysteresis on VUVLO(*3)                         | V <sub>UVLO</sub> hys    | IN=H → L                                                                                       |      | 100  |      | mV        |

| Overvoltage protection                          | Vovp                     | IN=L → H                                                                                       | 5.6  | 5.7  | 5.8  | V         |

| Hysteresis on Vove(*3)                          | V <sub>ovP</sub> hys     | IN=H → L                                                                                       |      | 175  |      | mV        |

| Input power detection voltage                   | VIN(DET)                 | BAT=3.6V, IN=L $\rightarrow$ H<br>Input power detect<br>when IN $\ge$ BAT+V <sub>IN(DET)</sub> | 50   | 80   | 130  | mV        |

| Hysteresis on $V_{IN(DET)}(*3)$                 | V <sub>IN(DET)</sub> hys | BAT=3.6V, IN=H → L                                                                             | 20   | 35   | 50   | mV        |

| Input power detection deglitch time(*3)         | t <sub>DGL(IN)</sub>     | Time measured from<br>IN=0 → 5V(1us rise-time)<br>to INGOOD="L"                                |      | 1.0  |      | ms        |

| Overvoltage blanking time(*3)                   | t <sub>DGL(OVP)</sub>    |                                                                                                |      | 50   |      | us        |

| OVP recovery deglitch time(*3)                  | tdgl(rec)                | Time measured from<br>IN=10 → 5V(1us fall-time)<br>to INGOOD="L"                               |      | 1.0  |      | ms        |

| Input power loss to OUT turn-off delay time(*3) | t <sub>DELAY</sub>       | BAT=3.6V<br>Time measured from<br>IN=5 $\rightarrow$ 3V(1us fall-time) to<br>INGOOD="H"        |      | 10   |      | ms        |

| Thermal shutdown temperature(*3)                | Tj <sub>(TSD)</sub>      | Tj=L → H                                                                                       |      | 150  |      | °C        |

| Hysteresis on Tj <sub>(TSD)</sub> (*3)          | Tj <sub>(TSD)</sub> hys  | Tj=H → L                                                                                       |      | 30   |      | °C        |

(\*3) Guaranteed by design

| Item                                     | Symbol                     | Measurement conditions                                             | Min.   | Тур.            | Max.   | Units |  |

|------------------------------------------|----------------------------|--------------------------------------------------------------------|--------|-----------------|--------|-------|--|

| SYSTEM-PATH · BATTERY-PATH               | SYSTEM-PATH · BATTERY-PATH |                                                                    |        |                 |        |       |  |

|                                          | I <sub>LIM1</sub>          | OUT=3.6V                                                           | 80     | 90              | 100    | mA    |  |

| Input current limit                      | I <sub>LIM2</sub>          | OUT=3.6V                                                           | 450    | 475             | 500    | mA    |  |

|                                          | I <sub>LIM3</sub>          | OUT=3.6V                                                           |        | Kilim<br>/Rilim |        | А     |  |

| ILIM setting current range(*4)           | ILIM(RNG)                  |                                                                    | 200    |                 | 1,500  | mA    |  |

| ILIM setting factor                      | KILIM                      | Ілмз=1А                                                            | 72,000 | 80,000          | 88,000 | AΩ    |  |

| ON resistance of System-path(*4)         | Ron(sys)                   |                                                                    |        | 200             | 300    | mΩ    |  |

| ON resistance of Battery-path(*4)        | Ron(BAT)                   |                                                                    |        | 50              | 75     | mΩ    |  |

| Voltage of input current limit operation | VINSPM                     |                                                                    | 4.35   | 4.50            | 4.63   | V     |  |

| OUT pin short detection voltage          | V <sub>OUT(SC)</sub>       |                                                                    | 0.8    | 0.95            | 1.1    | V     |  |

| Battery support voltage(*4)              | VSUP                       | V <sub>SUP</sub> =OUT-BAT when<br>Battery support mode<br>BAT=3.8V | 150    |                 | 300    | mV    |  |

(Except where noted otherwise : Ta=25 $^\circ\!C$  , IN=5V )

(\*4) Guaranteed by design

|                                             |                        | (Ex                                                  | cept where r | noted otherw                  | ise : Ta=25° | C,IN=5V) |  |

|---------------------------------------------|------------------------|------------------------------------------------------|--------------|-------------------------------|--------------|----------|--|

| Item                                        | Symbol                 | Measurement conditions                               | Min.         | Тур.                          | Max.         | Units    |  |

| CHARGE CONTROL                              |                        |                                                      |              |                               |              |          |  |

| Initialize time(*5)                         | t <sub>INIT</sub>      | 1clk=Tosc                                            |              | 2                             |              | clk      |  |

| Fast charge current setting range(*5)       | ICHG(RNG)              | This is applied to "1 of ISET"                       | 200          |                               | 1,500        | mA       |  |

| Fast charge current                         | IFSTCHG                | This is applied to "1 of ISET"                       |              | K <sub>ISET</sub><br>/RISET   |              | А        |  |

| Fast charge current setting factor          | KISET                  | R <sub>ISET</sub> =160k<br>I <sub>CHG</sub> ≧ 200mA  | 76,000       | 80,000                        | 84,000       | AΩ       |  |

| Fast charge current accuracy @small current | I <sub>ACC</sub>       | R <sub>ISET</sub> =160kΩ<br>I <sub>CHG</sub> < 200mA | -10          |                               | +10          | mA       |  |

| Pre-charge current                          | IPRECHG                |                                                      |              | K <sub>PRECHG</sub><br>/RISET |              | А        |  |

| Pre-charge current setting factor           | KPRECHG                | $R_{ISET}=160k\Omega$                                | 6,000        | 8,000                         | 10,000       | AΩ       |  |

| Relief charge current                       | IRELCHG                |                                                      | 4            | 8.5                           | 13           | mA       |  |

| End-of-charge current setting               | I                      | USB 500mA or ILIM mode                               | 20           |                               | 200          | mA       |  |

| range(*5)                                   | TERM(RNG)              | USB 100mA mode                                       | 6.7          |                               | 66.7         | mA       |  |

| End-of-charge detection current             | I <sub>TERM</sub>      |                                                      |              | Kiterm<br>/Riterm             |              | А        |  |

| End-of-charge detection current             | K                      | USB 500mA or ILIM mode $R_{ITERM}$ =160k $\Omega$    | 6,000        | 8,000                         | 10,000       | AΩ       |  |

| setting factor                              | Kiterm                 | USB 100mA mode<br>R <sub>ITERM</sub> =160kΩ          | 2,000        | 2,667                         | 3,333        | AΩ       |  |

| End-of-charge detection deglitch time(*5)   | t <sub>DGL(TERM)</sub> | 1clk=T <sub>osc</sub>                                |              | 8                             |              | clk      |  |

| BAT pull current(*5)                        | IPULL                  |                                                      |              | 80                            |              | mA       |  |

| BAT pull time(*5)                           | t <sub>BAT(DET)</sub>  |                                                      |              | 32                            |              | ms       |  |

(\*5) Guaranteed by design

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

|                                                        |                      | (Except where noted otherwise: Ta=25°C, IN=5 |      |                            |      |       |  |

|--------------------------------------------------------|----------------------|----------------------------------------------|------|----------------------------|------|-------|--|

| Item                                                   | Symbol               | Measurement conditions                       | Min. | Тур.                       | Max. | Units |  |

| Start voltage of pre-charge                            | V <sub>PRE</sub>     | BAT=L → H                                    | 1.9  | 2.0                        | 2.1  | V     |  |

| Hysteresis on VPRE(*6)                                 | $V_{PRE}$ hys        | BAT=H → L                                    |      | 100                        |      | mV    |  |

| Start voltage of fast-charge                           | V <sub>FST</sub>     | BAT=L → H                                    | 2.7  | 2.8                        | 2.9  | V     |  |

| Hysteresis on V <sub>FST</sub> (*6)                    | V <sub>FST</sub> hys | BAT=H → L                                    |      | 100                        |      | mV    |  |

| Pre-charge to fast charge transition deglitch time(*6) | <b>t</b> ptof        | 1clk=T <sub>osc</sub>                        |      | 16                         |      | clk   |  |

|                                                        | V <sub>BAT1</sub>    |                                              | 4.17 | 4.20                       | 4.23 | V     |  |

| Constant voltage control                               | V <sub>BAT2</sub>    |                                              | 4.12 | 4.15                       | 4.18 | V     |  |

| (VBAT1>VBAT2>VBAT3>VBAT4)                              | V <sub>BAT3</sub>    |                                              | 4.07 | 4.10                       | 4.13 | V     |  |

|                                                        | $V_{BAT4}$           |                                              | 4.02 | 4.05                       | 4.08 | V     |  |

| Voltage of recharge detection                          | $V_{\text{RECHG}}$   |                                              |      | V <sub>BAT</sub><br>-0.20V |      | V     |  |

| Voltage of charge current limit operation              | VOUTBPM              |                                              | 4.15 | 4.20                       | 4.25 | V     |  |

| Thermal regulation temperature(*6)                     | Tj <sub>(REG)</sub>  |                                              | 85   | 100                        | 115  | C°    |  |

(\*6) Guaranteed by design

|                                            |                         |                                     | (Except when | re noted other | wise : Ta=25 | ℃,IN=5V)          |

|--------------------------------------------|-------------------------|-------------------------------------|--------------|----------------|--------------|-------------------|

| Item                                       | Symbol                  | Measurement conditions              | Min.         | Тур.           | Max.         | Units             |

| BATTERY TEMPERATURE DETEC                  | TION                    | •                                   |              |                |              | •                 |

| VREF pin output voltage                    | V <sub>REF</sub>        |                                     | 2.74         | 2.80           | 2.86         | V                 |

| VREF pin source current ability            | I <sub>REF</sub>        | Decrease to 98% of $V_{\text{REF}}$ | 2            |                |              | mA                |

| VREF pin leakage current                   | I <sub>VREF(LEAK)</sub> | V <sub>REF</sub> =3.1V              |              |                | 1            | uA                |

| Battery removal detection TS pin voltage   | $V_{\text{TBR}}$        | TS=L → H                            | 85.0         | 90.0           | 95.0         | %V <sub>REF</sub> |

|                                            | <b>V</b> T10            | T1 detection<br>TS=L → H            | 76.6         | 78.1           | 79.6         | $%V_{REF}$        |

| Battery temperature detection TS           | <b>V</b> <sub>T20</sub> | T2 detection<br>TS=L → H            | 66.2         | 67.7           | 69.2         | $%V_{REF}$        |

| pin voltage                                | V <sub>T30</sub>        | T3 detection<br>TS=H → L            | 27.5         | 29.0           | 30.5         | %V <sub>REF</sub> |

| when I <sup>2</sup> C 05h b07= "0"         | <b>V</b> <sub>T40</sub> | T4 detection<br>TS=H → L            | 23.4         | 24.9           | 26.4         | %V <sub>REF</sub> |

|                                            | <b>V</b> T50            | T5 detection<br>TS=H → L            | 16.7         | 18.2           | 19.7         | %V <sub>REF</sub> |

|                                            | <b>V</b> <sub>T11</sub> | T1 detection<br>TS=L → H            | 71.6         | 73.1           | 74.6         | $%V_{REF}$        |

| Battery temperature detection TS           | <b>V</b> <sub>T21</sub> | T2 detection<br>TS=L → H            | 62.7         | 64.2           | 65.7         | $%V_{\text{REF}}$ |

| pin voltage                                | <b>V</b> <sub>T31</sub> | T3 detection<br>TS=H → L            | 31.5         | 33.0           | 34.5         | $%V_{\text{REF}}$ |

| when I <sup>2</sup> C 05h b07= "1"         | <b>V</b> <sub>T41</sub> | T4 detection<br>TS=H → L            | 27.9         | 29.4           | 30.9         | %V <sub>REF</sub> |

|                                            | <b>V</b> <sub>T51</sub> | T5 detection<br>TS=H → L            | 21.7         | 23.2           | 24.7         | %V <sub>REF</sub> |

| Hysteresis on TS pin voltage detection(*7) | V⊤shys                  |                                     |              | 2              |              | $%V_{\text{REF}}$ |

| TS pin leakage current                     | I <sub>TS(LEAK)</sub>   | TS=3.1V                             |              |                | 1            | uA                |

(\*7) Guaranteed by design

| (Except where noted otherwise : Ta=25°C , IN=5 |                             |                                                                                        |       |                         |       |       |  |

|------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------|-------|-------------------------|-------|-------|--|

| Item                                           | Symbol                      | Measurement conditions                                                                 | Min.  | Тур.                    | Max.  | Units |  |

| OSCILLATOR                                     |                             |                                                                                        |       |                         |       |       |  |

| Oscillation period                             | Tosc                        | $\begin{array}{l} R_{\text{ISET}} = 160 k\Omega \\ C_{\text{TMR}} = 15 nF \end{array}$ | 4.2   | 6.0                     | 7.8   | ms    |  |

| Pre-charge timer(*8)                           | TPRE                        | T <sub>BASE</sub> =T <sub>OSC</sub> ×2 <sup>20</sup><br>I <sup>2</sup> C default       |       | TBASE                   |       | s     |  |

| Total charge timer(*8)                         | T <sub>TOTAL</sub>          | T <sub>BASE</sub> =T <sub>OSC</sub> ×2 <sup>20</sup><br>I <sup>2</sup> C default       |       | 6<br>×Т <sub>вазе</sub> |       | s     |  |

| USB DETECTION                                  |                             |                                                                                        |       |                         |       |       |  |

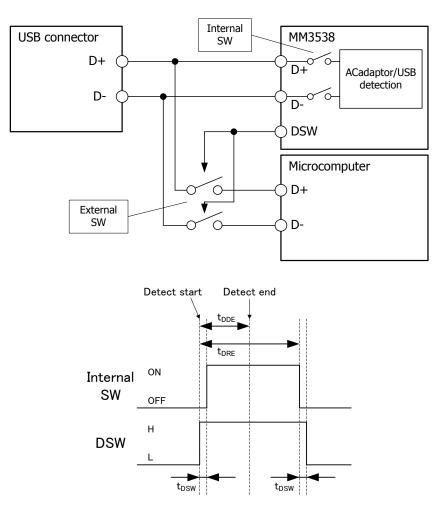

| D+/D- detection time(*8)                       | t <sub>DDE</sub>            |                                                                                        |       | 128                     |       | ms    |  |

| D+/D- detection-sw release time(*8)            | t <sub>DRE</sub>            |                                                                                        |       | 256                     |       | ms    |  |

| Dead time of D+/D-detection(*8)                | tosw                        |                                                                                        |       | 1                       |       | ms    |  |

| DSW pin sink current ability                   | $V_{\text{DSW}(\text{SI})}$ | I <sub>SINK</sub> =1mA<br>when DSW="L"                                                 |       |                         | 0.25  | V     |  |

| DSW pin source current ability(*8)             | V <sub>DSW(SO)</sub>        | I <sub>SOURCE</sub> =1mA<br>when DSW="H"                                               | 4.50  |                         |       | V     |  |

| Bias at D+ pin(*8)                             | V <sub>D+</sub>             | can source at least<br>150uA                                                           | 0.475 | 0.600                   | 0.700 | V     |  |

| D+ pin output current limit(*8)                | I <sub>D+</sub>             | D+=0V                                                                                  |       |                         | 1.5   | mA    |  |

| D-pin sink current(*8)                         | I <sub>D-</sub>             | D-=0.5V                                                                                | 10    | 30                      | 50    | uA    |  |

| D+ pin leakage current                         | I <sub>D+(LEAK)</sub>       | not in detection mode                                                                  |       |                         | 1     | uA    |  |

| D-pin leakage current                          | ID-(LEAK)                   | not in detection mode                                                                  |       |                         | 1     | uA    |  |

| D+/D- comparator threshold                     | V <sub>DC</sub>             | L→H                                                                                    | 0.35  | 0.40                    | 0.45  | V     |  |

| D+/D-Hysterisis on V <sub>DC</sub> (*8)        | V <sub>DC</sub> hys         | H→L                                                                                    |       | 42                      |       | mV    |  |

(\*8) Guaranteed by design

|                                     |                     |                                        |      | e noted otherw | lise: Ta=250 | , IN-5V) |

|-------------------------------------|---------------------|----------------------------------------|------|----------------|--------------|----------|

| Item                                | Symbol              | Measurement conditions                 | Min. | Тур.           | Max.         | Units    |

| OUTGOOD PIN                         |                     |                                        |      |                |              |          |

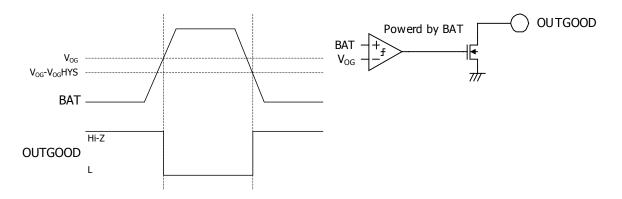

| OUTGOOD threshold                   | V <sub>OG</sub>     | BAT=L → H                              | 2.89 | 2.95           | 3.01         | V        |

| Hysterisis on V <sub>OG</sub> (*9)  | V <sub>og</sub> hys | BAT=H → L                              |      | 0.15           |              | V        |

| LOGIC INPUT AND OUTPUT              |                     |                                        |      |                |              |          |

| Low level input voltage             | VL                  | SYSOFF, OCD,<br>SDA, SCL               |      |                | 0.4          | V        |

| High level input voltage            | V <sub>H</sub>      | SYSOFF, OCD,<br>SDA, SCL               | 1.5  |                |              | V        |

| Built-in pull-down resistor value   | R <sub>PD</sub>     | SYSOFF, OCD                            |      | 100            |              | kΩ       |

| Open drain pin sink current ability | Vopd                | I <sub>sınк</sub> =5mA<br>when Pin="L" |      |                | 0.25         | V        |

(Except where noted otherwise : Ta=25 $^{\circ}$ C , IN=5V )

(\*9) Guaranteed by design

|                                |                       |                        | (Except where | e noted otherw | rise : Ta=25℃ | , IN=5V ) |

|--------------------------------|-----------------------|------------------------|---------------|----------------|---------------|-----------|

| Item                           | Symbol                | Measurement conditions | Min.          | Тур.           | Max.          | Units     |

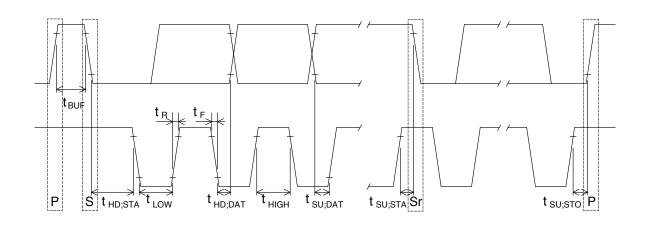

| I <sup>2</sup> C BUS           |                       |                        |               |                |               |           |

| Clock frequency                | f <sub>sc∟</sub>      |                        | 10            |                | 400           | kHz       |

| Data transfer wait time(*10)   | t <sub>BUF</sub>      |                        | 1.3           |                |               | us        |

| SCL start hold time(*10)       | t <sub>hd;sta</sub>   |                        | 0.6           |                |               | us        |

| SCL low level hold time(*10)   | t∟ow                  |                        | 1.3           |                |               | us        |

| SCL high level hold time(*10)  | tнigн                 |                        | 0.6           |                |               | us        |

| Start condition setup(*10)     | t <sub>su;sta</sub>   |                        | 0.6           |                |               | us        |

| SDA data hold time(*10)        | $\mathbf{t}_{HD;DAT}$ |                        | 100           |                |               | ns        |

| SDA data setup time(*10)       | tsu;dat               |                        | 100           |                |               | ns        |

| SDA,SCL rise time(*10)         | t <sub>R</sub>        |                        |               |                | 300           | ns        |

| SDA,SCL fall time(*10)         | t⊧                    |                        |               |                | 300           | ns        |

| Stop condition setup time(*10) | <b>t</b> su;sто       |                        | 0.6           |                |               | us        |

(\*10) Guaranteed by design

### Function

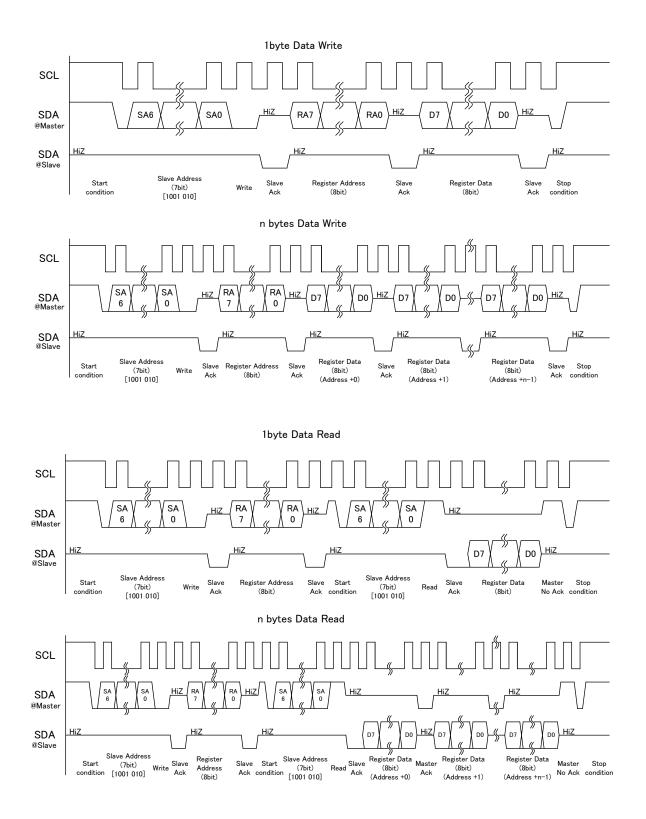

#### (1) ABOUT I<sup>2</sup>C BUS

I<sup>2</sup>C BUS is inter bus system controlled by 2 lines (SDA,SCL). Data are transmitted and received in the units of byte and Acknowledge. It is transmitted by MSB first from the Start condition.

The data format is set as shown in the following figure.

#### (2) I<sup>2</sup>C REGISTER MAP

|                  | b07 b06 b05 b04          |                         | b04           | b03 b02      |                     | b01           | b00               |                           |                |

|------------------|--------------------------|-------------------------|---------------|--------------|---------------------|---------------|-------------------|---------------------------|----------------|

| Slave<br>Address |                          | 1                       | 0             | 0            | 1                   | 0             | 1                 | 0                         | R = 1<br>W = 0 |

|                  | 01h                      | CV Setting              | (T1 ~ T2)     | CV Setting   | (T2 ~ T3)           | CV Setting    | CV Setting        | CV Setting (T4 $\sim$ T5) |                |

|                  |                          | R/W                     | R/W           | R/W          | R/W                 | R/W           | R/W               | R/W                       | R/W            |

|                  | 02h<br>03h<br>04h<br>05h | CC S                    | Setting (T1 - | ~ T2)        | CC S                | Setting (T2 - | Charge<br>Enable  | SAL<br>Release            |                |

| ess              |                          | R/W                     | R/W           | R/W          | R/W                 | R/W           | R/W               | R/W                       | W              |

| Register Address |                          | cc s                    | Setting (T3 - | ~ T4)        | cc s                | Setting (T4 - | USB Current Limit |                           |                |

| gist             |                          | R/W                     | R/W           | R/W          | R/W                 | R/W           | R/W               | R/W                       | R/W            |

| Be               |                          | 04h Battery Temperature |               | ature        | Charger<br>Time-out |               |                   | ISET<br>Short             | ADP/USB        |

|                  |                          | R                       | R             | R            | R                   | R             | R                 | R                         | R              |

|                  |                          | NTC                     | Pre           | e-charge Tir | mer                 | Tota          | al charge Ti      | mer                       |                |

|                  |                          | R/W                     | R/W           | R/W          | R/W                 | R/W           | R/W               | R/W                       | R              |

R : Read Only (Write data is ignored) W : Writable ("0" is returned for read-in) R/W : Readable and Writable

#### (3) I<sup>2</sup>C REGISTER EXPLANATION

| R/W     | CV Setting (T1 $\sim$ T2) |                           |     |         |  | R/W     |                           | ~ T3)   |     |         |  |

|---------|---------------------------|---------------------------|-----|---------|--|---------|---------------------------|---------|-----|---------|--|

| 01h     | b07                       | b                         | 06  | V       |  | 01h     | b05                       | b       | 04  | V       |  |

| default | 0                         | (                         | 0   | 4.05    |  | default | 0                         | (       | 0   | 4.05    |  |

|         | 0                         |                           | 1   | 4.10    |  |         | 0                         |         | 1   | 4.10    |  |

|         | 1                         | (                         | 0   | 4.15    |  |         | 1                         |         | 0   | 4.15    |  |

|         | 1                         |                           | 1   | 4.20    |  |         | 1                         |         | 1   | 4.20    |  |

| R/W     | W CV Setting (T3 ~ T4)    |                           |     |         |  |         | CV Setting (T4 $\sim$ T5) |         |     |         |  |

| 01h     | b03                       | -                         | 02  | V       |  | 01h     | b01                       | r • • • |     | V V     |  |

| default | 0                         | (                         | 0   | 4.05    |  | default | 0                         | (       | 0   | 4.05    |  |

|         | 0                         |                           | 1   | 4.10    |  |         | 0                         |         | 1   | 4.10    |  |

|         | 1                         | (                         | 0   | 4.15    |  |         | 1                         | (       | 0   | 4.15    |  |

|         | 1                         |                           | 1   | 4.20    |  |         | 1                         |         | 1   | 4.20    |  |

| R/W     | (                         | CC Setting (T1 $\sim$ T2) |     |         |  | R/W     | CC Setting (T2 $\sim$ T3) |         |     |         |  |

| 02h     | b07                       | b06                       | b05 | of ISET |  | 02h     | b04                       | b03     | b02 | of ISET |  |

| default | 0                         | 0                         | 0   | 1/8     |  | default | 0                         | 0       | 0   | 1/8     |  |

|         | 0                         | 0                         | 1   | 2/8     |  |         | 0                         | 0       | 1   | 2/8     |  |

|         | 0                         | 1                         | 0   | 3/8     |  |         | 0                         | 1       | 0   | 3/8     |  |

|         | 0                         | 1                         | 1   | 4/8     |  |         | 0                         | 1       | 1   | 4/8     |  |

|         | 1                         | 0                         | 0   | 5/8     |  |         | 1                         | 0       | 0   | 5/8     |  |

|         | 1                         | 0                         | 1   | 6/8     |  |         | 1                         | 0       | 1   | 6/8     |  |

|         | 1                         | 1                         | 0   | 7/8     |  |         | 1                         | 1       | 0   | 7/8     |  |

|         | 1                         | 1                         | 1   | 1       |  |         | 1                         | 1       | 1   | 1       |  |

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

| R/W     |     | 00.50 | tting (T3 | a. T1)          | R/W      |  |  |

|---------|-----|-------|-----------|-----------------|----------|--|--|

| 03h     | b07 | b06   | b05       | 03h             |          |  |  |

| default | 0   | 000   | 0         | of ISET<br>1/8  | default  |  |  |

| uelault | 0   | 0     | 1         | 2/8             | uelault  |  |  |

|         |     | 1     |           | 3/8             |          |  |  |

|         | 0   |       | 0         |                 |          |  |  |

|         | 0   | 1     | 1         | 4/8             |          |  |  |

|         | -   | 0     | 0         | 5/8             |          |  |  |

|         | 1   | 0     | 1         | 6/8             |          |  |  |

|         | 1   | 1     | 0         | 7/8             |          |  |  |

|         | 1   | 1     | 1         | 1               |          |  |  |

| R/W     |     | Cha   | arge Ena  | ble             | R/W      |  |  |

| 02h     | b01 |       |           | atus            | 02h      |  |  |

| default | 0   |       | No d      | charge          | default  |  |  |

|         | 1   |       | Cha       | arging          |          |  |  |

| R/W     |     |       | LISB (    | Current Limit   |          |  |  |

| 03h     | b01 | b00   |           | Maximum input c | urrent   |  |  |

| default | 0   | 0     |           | 00mA. USB 100m  |          |  |  |

| uelault | 0   | 1     |           | 00mA. USB 500m  |          |  |  |

|         | 1   | 0     | 50        | ILIM Setting    |          |  |  |

|         | 1   | 1     | Sta       | ndby(USB suspe  |          |  |  |

|         | I   | I     |           |                 | nu moue) |  |  |

| R       |     |       |           | Temperature     |          |  |  |

| 04h     | b07 | b06   | b05       | Stat            |          |  |  |

|         | 0   | 0     | 0         | Battery not     |          |  |  |

|         | 0   | 0     | 1         | ~ 1             |          |  |  |

|         | 0   | 1     | 0         | T1 ~            | T2       |  |  |

|         | 0   | 1     | 1         | T2 ~            | Т3       |  |  |

|         | 1   | 0     | 0         | T3 ~            | T4       |  |  |

|         | 1   | 0     | 1         | T4 ~            | T5       |  |  |

|         | 1   | 1     | 0         | T5 ·            | ~        |  |  |

| R       |     | Char  | ger Time  |                 | R        |  |  |

| 04h     | b04 |       |           | atus            | 04h      |  |  |

| 0411    | 0   |       |           | ormal           | 0411     |  |  |

|         | 1   |       |           | ne-out          |          |  |  |

|         |     |       |           |                 |          |  |  |

| R       |     | []    | _IM Shor  |                 | R        |  |  |

| 04h     | b02 |       | St        | atus            | 04h      |  |  |

|         | 0   |       |           | ormal           |          |  |  |

|         | 1   |       | S         | hort            |          |  |  |

| R       |     | A     | ADP/USB   | <u> </u>        | R/W      |  |  |

| 04h     | b00 | ,<br> |           | atus            | 05h      |  |  |

| V III   | 0   |       |           | Power           |          |  |  |

|         | 1   |       |           | Power           | default  |  |  |

| =       |     |       |           |                 |          |  |  |

| R/W     |     |       | charge Ti |                 | R/W      |  |  |

| 05h     | b06 | b05   | b04       | of TBASE        | 05h      |  |  |

| default | 0   | 0     | 0 1       |                 |          |  |  |

|         | 0   | 0     | 1 2       |                 |          |  |  |

|         | 0   | 1     | 0         | 3               |          |  |  |

|         | 0   | 1     | 1         | 4               |          |  |  |

|         | 1   | 0     | 0         | 5               | default  |  |  |

|         | 1   | 0     | 1         | 6               |          |  |  |

|         | 1   | 1     | 0         | 7               |          |  |  |

|         | 1   | 1     | 1         | No timer        |          |  |  |

|         |     |       |           |                 |          |  |  |

| R/W     | CC Setting (T4 $\sim$ T5) |     |     |         |  |  |  |

|---------|---------------------------|-----|-----|---------|--|--|--|

| 03h     | b04                       | b03 | b02 | of ISET |  |  |  |

| default | 0                         | 0   | 0   | 1/8     |  |  |  |

|         | 0                         | 0   | 1   | 2/8     |  |  |  |

|         | 0                         | 1   | 0   | 3/8     |  |  |  |

|         | 0                         | 1   | 1   | 4/8     |  |  |  |

|         | 1                         | 0   | 0   | 5/8     |  |  |  |

|         | 1                         | 0   | 1   | 6/8     |  |  |  |

|         | 1                         | 1   | 0   | 7/8     |  |  |  |

|         | 1                         | 1   | 1   | 1       |  |  |  |

| R/W     | SAL Release               |     |     |         |  |  |  |

| R/W     | SAL Release |         |  |  |  |  |

|---------|-------------|---------|--|--|--|--|

| 02h     | b00         | Status  |  |  |  |  |

| default | 0           | Normal  |  |  |  |  |

|         | 1           | Release |  |  |  |  |

Input OVP

ISET Short

NTC

Status Normal

OVP

Status

Normal

Short

Status

b03

0 1

b01

0

1

b07

| Juiuo   |          |  | 0011    | 501                |   | 014140              |     |                      |  |

|---------|----------|--|---------|--------------------|---|---------------------|-----|----------------------|--|

| 3 Power |          |  |         | 0                  |   | for NCP15WF104F03RC |     |                      |  |

| Power   |          |  | default | 1                  |   | for NCP15XH103F03RC |     |                      |  |

| Timer   |          |  | R/W     | Total Charge Timer |   |                     |     |                      |  |

|         | of TBASE |  | 05h     | b03                | ł | b02                 | b01 | of T <sub>BASE</sub> |  |

|         | 1        |  |         | 0                  |   | 0                   | 0   | 2                    |  |

|         | 2        |  |         | 0                  |   | 0                   | 1   | 3                    |  |

|         | 3        |  |         | 0                  |   | 1                   | 0   | 4                    |  |

|         | 4        |  |         | 0                  |   | 1                   | 1   | 5                    |  |

|         | 5        |  | default | 1                  |   | 0                   | 0   | 6                    |  |

|         | 6        |  |         | 1                  |   | 0                   | 1   | 7                    |  |

|         | 7        |  |         | 1                  |   | 1                   | 0   | 8                    |  |

|         | No timer |  |         | 1                  |   | 1                   | 1   | No timer             |  |

|         |          |  |         |                    |   |                     |     |                      |  |

| Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications. |

#### (4) POWER SUPPLY INPUT

MM3538 normal operation starts when all the following conditions are met, and determined that the normal power supply is connected.

$\begin{array}{l} (1) \text{ IN } > \text{VUVLO} \\ (2) \text{ IN } > \text{BAT + VIN(DET)} \\ (3) \text{ IN } < \text{VOVP} \end{array}$

INGOOD pin is NchMOS open drain output. Open drain MOS is turned on when the normal powersupply is connected.

When power is not entered, MM3538 has been on the path to the battery to supply power from the battery to OUT pin.

#### (5) OUTGOOD PIN

OUTGOOD pin is NchMOS open drain output. When BAT pin voltage becomes higher than 2.95V (=VOG), open drain MOS is turned on. Moreover, this function operates on the voltage from BAT pin. For the reason, it operates by battery only.

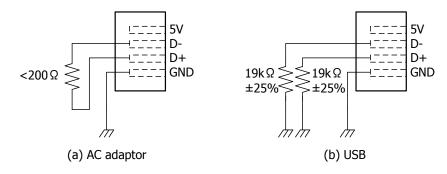

#### (6) AC ADAPTOR • USB DETECTION

An AC adaptor and USB bus have composition as shown in each following figure. MM3538 uses D+ pin / D- pin, judges automatically whether the inputted power supply is an AC adaptor or a USB bus, and operates an input limit. Moreover, a judgment result is displayed on an I<sup>2</sup>C register (= I<sup>2</sup>C 04h b00).

The internal SW is turned on after a power supply input, and detection is started, and detection is ended in 128ms (= tDDE) after. Furthermore, the inside SW is turned off in 128 ms after (a total of 256 ms (=tDRE)). When the inside SW is ON, a DSW terminal outputs "H". As shown in the following figure, it is used for ON/OFF control of the external SW. MM3538 and other ICs will not be simultaneously connected to a D+/D-line.

#### (7) IN CURRENT LIMIT

MM3538 restricts the system-path current which flows into IN pin.

When detected as USB, the input current limit is set by OCD pin. Then, it can change into other preset values using I<sup>2</sup>C control. Please refer to another section for OCD pin.

When detected as AC adaptor, the input current limit is set by ILIM pin. Then it can't change into other preset values using I2C control.

The setting current by ILIM pin is as follows.

$$I_{\text{LIMB}}\left[A\right] = \frac{K_{\text{ILIMB}}\left[A^{\bullet}\Omega\right]}{R_{\text{ILIM}}\left[\Omega\right]} = \frac{80,000 \left[A^{\bullet}\Omega\right]}{R_{\text{ILIM}}\left[\Omega\right]}$$

#### (8) OCD PIN

When detected as USB by the AC adaptor/USB detection, it is a terminal which sets up the initial value of an input current limit.

When OCD="L", input current limit is set to 100mA.

When OCD="H", input current limit is set to 500mA.

Although an initial value is set up with the above-mentioned value, it can be changed into other preset values after that using I2C control. OCD pin is a terminal which sets up an initial value, after power activation, cannot change a preset value by OCD pin.

#### (9) IN pin voltage control System-path management (IN-SPM)

MM3538 will decrease an input limit, if IN terminal voltage turns into voltage lower than 4.5V (=VINSPM). Moreover, charge operation is stopped. This function becomes effective only when an input power source is detected as USB, and it prevents crash of USB bus of the host side.

#### (10) SYSOFF PIN

It is possible to turn off a system-path compulsorily by making SYSOFF pin into "H".

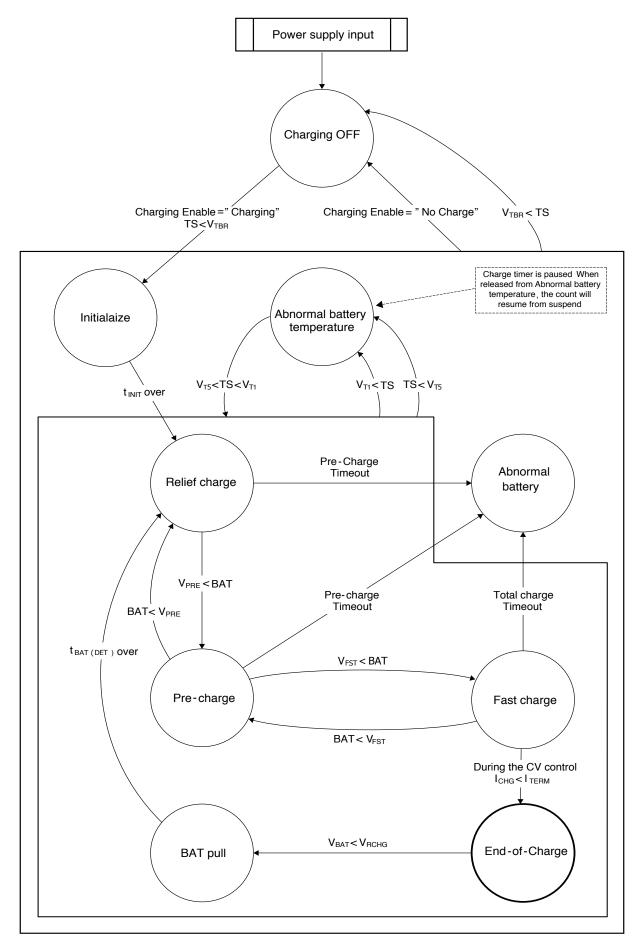

#### (11) CHARGE CONTROL

Charge is started by making ChargeEnable (= $I^2C$  02h b01) into "Charging" in the state where there are an input power source and a Li-ion battery. Pre-charge current and Fast charge current will be set up using an ISET pin, and Pre-charge current will be 1/10 of Fast charge current. End-of-charge detection current is set up using ITERM pin. When an input limit is in 100mA mode, End-of-charge detection current is set to one third of the preset values in an ITERM pin. The setting current in ISET pin and ITERM pin is as follows.

$$I_{FSTCHG}[A] = \frac{K_{ISET}[A \cdot \Omega]}{R_{ISET}[\Omega]} = \frac{80,000 [A \cdot \Omega]}{R_{ISET}[\Omega]}$$

$$I_{PRECHG}[A] = \frac{I_{FSTCHG}[A]}{10} = \frac{K_{ISET}[A \cdot \Omega]}{10 \cdot R_{ISET}[\Omega]} = \frac{8,000 [A \cdot \Omega]}{R_{ISET}[\Omega]}$$

$$I_{TERM}[A] = \frac{K_{ITERM}[A \cdot \Omega]}{R_{ITERM}[\Omega]} = \frac{8,000 [A \cdot \Omega]}{R_{ITERM}[\Omega]}$$

Charging current is controlled by general CCCV control. However, charging current decreases during CC control at the following factor developmental time.

When OUT terminal voltage falls and the charging current limit function operates. When chip temperature rises and the thermal regulation function operates.

Charge is suspended when the abnormalities in battery temperature occur. And a charger timer stops. A charge timer stops at this time. When these factors are canceled, charge operation is resumed and a charge timer resumes too.

When Pre-charge timer or Total charge timer is time-up, remove power supply or remove battery or make ChargeEnable into "No charge" to reset.

CHG pin is NchMOS open drain output. While charging current is flowing, open drain MOS is turned on.

#### Charge Timing Chart Pre-charge (Re-charge) Status Initialaize Relief charge Pre-charge Fast charge End-of-charge BAT pull Fast charge (Re-charge) Charging **Charging Enable** No Charge I FSTCHG GL(TERM t<sub>PTOF</sub> t<sub>BAT(DET)</sub> t<sub>iNIT</sub> t<sub>PTOF</sub> Charge current I<sub>PRECHG</sub> I<sub>TERM</sub> I<sub>RELCHG</sub> 0mA - I<sub>PULL</sub> $V_{\text{BAT}}$ VRECHG BAT voltage $V_{FST}$ V PRE

Hi-Z

L

CHG pin

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

Charge State Machine

Any products mentioned in this catalog are subject to any modification in their appearance and others for improvements without prior notification.

The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications.

#### (12) CHARGE CURRENT LIMIT

When the sum total of OUT pin load current and charging current is larger than an input current limit, OUT pin voltage falls. If OUT pin voltage decreases from 4.2V (=VOUTBPM), charging current will be restricted and the fall of OUT pin voltage will be prevented. Charge status does not become full charge while this function is operating. Even if the charging current limit function operates and it restricts charging current to 0mA, when OUT pin voltage continues falling, the battery support function operates.

#### (13) THERMAL REGULATION

If the chip temperature of MM3538 rises during charge operation and it becomes  $100^{\circ}$ C (= Tj (REG)), charging current will be restricted and generation of heat will be prevented. Even if the thermal regulation function operates and it restricts charging current to 0mA, if chip temperature continues rising and chip temperature rises to  $150^{\circ}$ C (= Tj (TSD)), the thermal shutdown function will operate.

#### (14) THERMAL SHUTDOWN

In order to protect MM3538 from thermal destruction, the thermal shutdown circuit is built in, and if chip temperature rises to  $150^{\circ}C$  (=Tj(TSD)), it will be in a thermal shutdown state. A system-path is turn off, and a battery-path is turn ON during a thermal shutdown.

#### (15) CHARGE TIMER

For safety reservation of charge, MM3538 builds in the pre-charge timer and the total charge timer. judges with it being unusual with a timer passing the deadline of, and suspends charge. Charge is suspended when time-up happened. It is as follows during the count of each timer.

- Pre-charge timer : Relief charge + Pre-charge

- Total charge timer : Relief charge + Pre-charge + Fast charge

The clock frequency used by the pre-charge timer and a total charge timer is determined with the resistance of ISET pin and capacity of TMR pin.

$$T_{OSC}[s] = \frac{2 \cdot C_{TMR}[F]}{0.8 [V] / R_{ISET}[\Omega]}$$

$T_{BASE}[s] = T_{OSC}[s] \times 2^{20}$

The time of a pre-charge timer and a total charge timer sets up what time of the obtained base frequency (= TBASE) is used by I2C (=I2C 05h b06~b01).

During fast charge, when charging current decreases by operation of a charging current limit function, in roportion to the reduction rate, a clock frequency becomes small. For example, when a fast charge current setup is 500mA and it decreases to 250mA by the above-mentioned factor, a clock frequency is set to one half and, as a result, the time of a charge timer doubles.

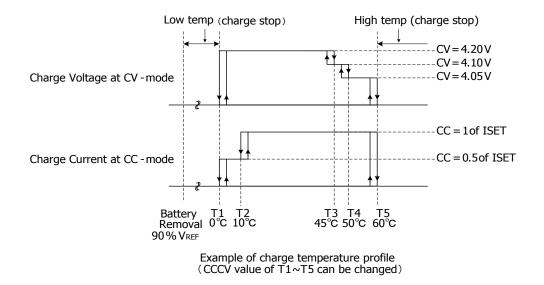

#### (16) CHARGE TEMPERATURE PROFILE

MM3538 corresponds to the charge temperature profile which JEITA recommends. Each CCCV value can be set up in four (T1 $\sim$ T2, T2 $\sim$ T3, T3 $\sim$ T4, and T4 $\sim$ T5) using I<sup>2</sup>C (=I<sup>2</sup>C 01h $\sim$ 03h). Moreover, MM3538 is optimized by the two following kinds of thermo sensitive registers, and can be chosen by I<sup>2</sup>C (=I<sup>2</sup>C 05h b07).

NCP15WF104F03RC (100kohm, 4250K, Murata Manufacturing)

NCP15XH103F03RC (10kohm, 3380K, Murata Manufacturing)

#### (17) SAL PIN

When the following factor occurs and the contents of the  $I^2C$  register change, a SAL terminal tells you. This pin is a NchMOS open drain output. When the contents of the  $I^2C$  register change, open drain MOS is turned on.

- (1) When battery-temp becomes low-temp ( $\sim$ T1) or high-temp (T5 $\sim$ ) (=I<sup>2</sup>C 04h b07 $\sim$ b05)

- 2 When pre-charge timer or total charge timer is time-up ( $=I^2C$  04h b04)

- (3) Input overvoltage protection function operates (= $I^2C$  04h b03)

- (4) When ILIM pin short to GND (= $I^2C$  04h b02)

- (5) When ISET pin short to GND (= $I^2C$  04h b01)

After a SAL pin becoming "L", in order to return to H", it is necessary to control SAL Release (= $I^2C$  02h b00). While it has been in the state which the above-mentioned factor generated, even if it performs SAL Release, since there is no change in the contents of the  $I^2C$  register, a SAL pin does not react again.

#### (18) BATTERY SUPPORT

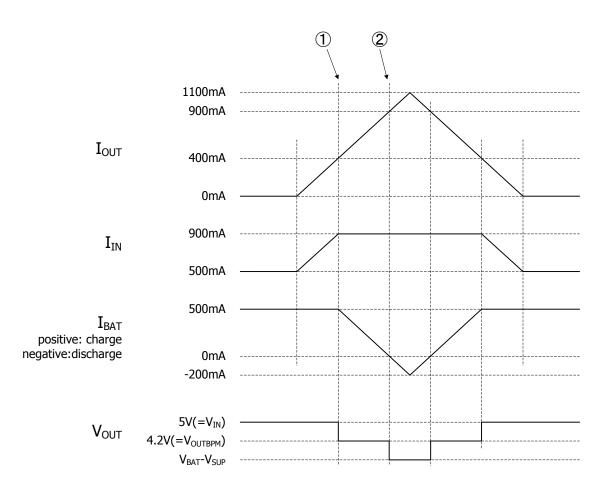

Although the current load of an OUT terminal is large and the charging current limit function is operating, a battery-path is turned on, if OUT terminal voltage continues falling and it falls from BAT-150~300mV(= $V_{SUP}$ ). By this, current will be supplied from both an input power source and a battery, and the fall of OUT terminal voltage is prevented. As an example, the timing chart at the time of the following setup is shown.

[ The example of a setting ] Charge Current setting = 500mA USB Current limit = 900mA (use ILIM pin)

The sum total of I<sub>OUT</sub> and I<sub>BAT</sub> becomes larger than 900mA, and V<sub>OUT</sub> falls by an input limit function. Simultaneously, the charging current limit operates and charging current decreases so that V<sub>OUT</sub> may not fall.

By a charging current limit function, even if it controls charging current to 0mA, when  $V_{\text{OUT}}$  falls, the battery support function operates and it prevents the fall of  $V_{\text{OUT}}$ .

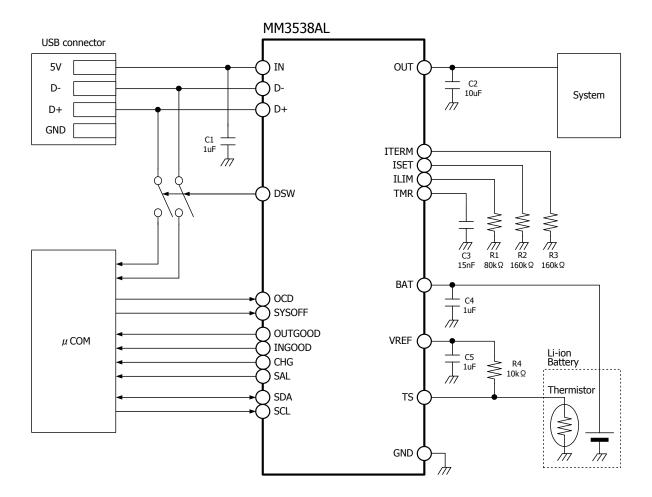

# Application Circuit

These circuits are typical examples provided for reference purposes, so in actual applications, the circuit constants, conditions and operations should be thoroughly studied.

Mitsumi Electric Co., Ltd. assumes no responsibility for any trouble or damage as a result of the use of these circuits.

Mitsumi Electric Co., Ltd. assumes no responsibility for any infringement of industrial property or any other right of a third party or us, as a result of the use of these circuits.